## UNIVERSITY OF TWENTE.

# P4 (Programming Protocol-independent Packet Processors) Lab

**Advanced Networking**

Friday Sep 5, 2025

#### P4 Lab

**Teaching Assistant**

Shyam Krishna Khadka (s.k.khadka@utwente.nl)

- Most of the contents are from

- P4 Language Consortium: "01 Introduction to Data Plane Programming (Stephen Ibanez)".

## Introduction

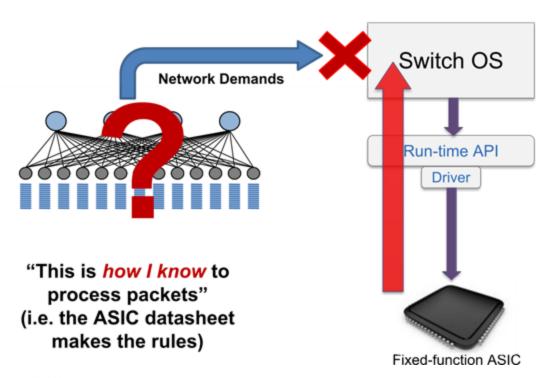

Status Quo: Bottom-up

UNIVERSITY OF TWENTE.

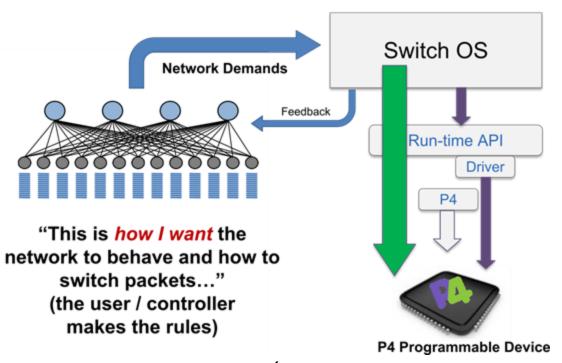

## Introduction

A Better Approach: Top-down design

p4.org

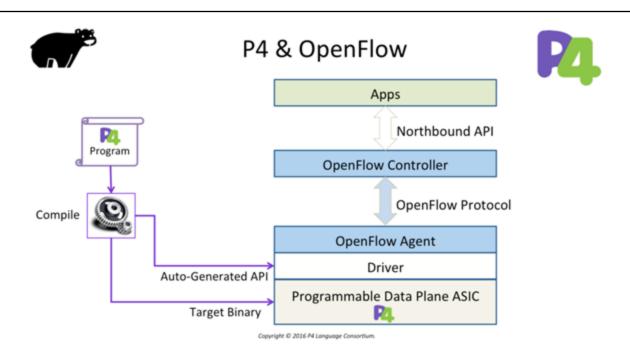

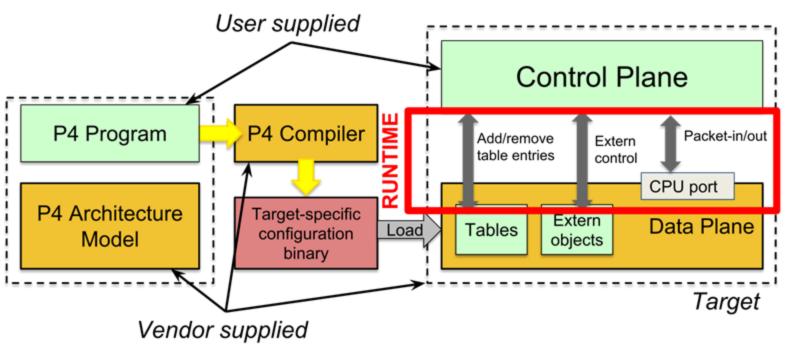

Control Plane & Data Plane

5

P4

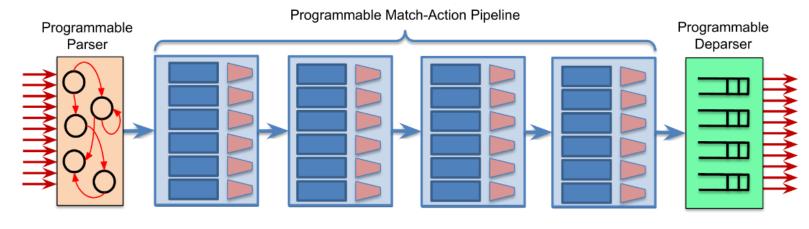

PISA: Protocol Independent Switch Architecture (e.g. Intel Tofino Switch)

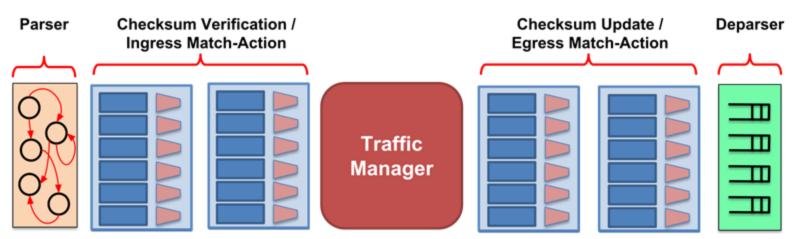

bmv2 Switch

- Used in the lab assignments

- For developing, testing and debugging

- V1Model: P4 Architecture model for bmv2

V1Model stages

V1Model stages

```

#include <core.p4>

#include <v1model.p4>

/* HEADERS */

struct metadata { ... }

struct headers {

ethernet t

ethernet;

ipv4 t

ipv4;

/* PARSER */

parser MyParser(packet in packet,

out headers hdr,

inout metadata meta,

inout standard metadata t smeta) {

/* CHECKSUM VERIFICATION */

control MyVerifyChecksum(in headers hdr,

inout metadata meta) {

/* INGRESS PROCESSING */

control MyIngress(inout headers hdr,

inout metadata meta,

inout standard metadata t std meta) {

```

```

/* EGRESS PROCESSING */

control MyEgress(inout headers hdr,

inout metadata meta,

inout standard metadata t std meta) {

/* CHECKSUM UPDATE */

control MyComputeChecksum(inout headers hdr,

inout metadata meta) {

/* DEPARSER */

control MyDeparser(inout headers hdr,

inout metadata meta) {

/* SWITCH */

V1Switch(

MyParser(),

MyVerifyChecksum(),

MyIngress(),

MyEgress(),

MyComputeChecksum(),

MyDeparser()

main;

```

Metadata and V1Model Standard Metadata

```

struct standard metadata t {

bit<9> ingress port;

bit<9> egress_spec;

bit<9> egress_port;

bit<32> clone_spec;

bit<32> instance type;

bit<1> drop;

bit<16> recirculate port;

bit<32> packet length;

bit<32> eng timestamp;

bit<19> eng qdepth;

bit<32> deq_timedelta;

bit<19> deg gdepth;

bit<48> ingress global timestamp;

bit<32> 1f field list;

bit<16> mcast grp;

bit<1> resubmit flag;

bit<16> egress rid;

bit<1> checksum error;

```

- ingress\_port the port on which the packet arrived

- egress\_spec the port to which the packet should be sent to

- egress\_port the port on which the packet is departing from (read only in egress pipeline)

UNIVERSITY OF TWENTE.

Basic example

```

#include <core.p4>

#include <v1model.p4>

struct metadata {}

struct headers {}

parser MyParser(packet in packet,

out headers hdr,

inout metadata meta,

inout standard metadata t standard metadata) {

state start { transition accept; }

control MyVerifyChecksum(inout headers hdr, inout metadata

meta) {

apply { } }

control MyIngress(inout headers hdr,

inout metadata meta,

inout standard metadata t standard metadata) {

apply {

if (standard metadata.ingress port == 1) {

standard metadata.egress spec = 2;

} else if (standard metadata.ingress port == 2) {

standard metadata.egress spec = 1;

```

```

control MyEgress(inout headers hdr,

inout metadata meta,

inout standard metadata t standard metadata) {

apply { }

control MyComputeChecksum(inout headers hdr, inout metadata

meta) {

apply { }

control MyDeparser(packet out packet, in headers hdr) {

apply { }

V1Switch(

MyParser(),

MyVerifyChecksum(),

MyIngress(),

MyEgress(),

MyComputeChecksum(),

MyDeparser()

main;

```

Basic example elaborated.

```

#include <core.p4>

#include <v1model.p4>

struct metadata {}

struct headers {}

parser MyParser(packet in packet, out headers hdr,

inout metadata meta,

inout standard metadata t standard metadata) {

state start { transition accept; }

control MyIngress(inout headers hdr, inout metadata meta,

inout standard metadata t standard metadata) {

action set egress spec(bit<9> port) {

standard metadata.egress spec = port;

table forward {

key = { standard metadata.ingress port: exact;

actions = {

set_egress_spec;

NoAction;

size = 1024;

default action = NoAction();

apply { forward.apply(); }

```

```

control MyEgress(inout headers hdr,

inout metadata meta,

inout standard_metadata_t standard_metadata) {

apply {

}

}

control MyVerifyChecksum(inout headers hdr, inout metadata meta) {

apply {

}

}

control MyComputeChecksum(inout headers hdr, inout metadata meta) {

apply {

}

}

control MyDeparser(packet_out packet, in headers hdr) {

apply {

}

}

V1Switch( MyParser(), MyVerifyChecksum(), MyIngress(), MyEgress(), MyComputeChecksum(), MyDeparser() ) main;

```

| Key | Action ID          | Action Data |

|-----|--------------------|-------------|

| 1   | set_egress_spec ID | 2           |

| 2   | set_egress_spec ID | 1           |

Parsing

- extern: interface for functionality provided by switch vendor

- Similar to abstract classes/methods in OOP

- State machine

- Transitions

- select: change state

- accept: finish parsing

#### Parsing // packet\_in: extern for input packet extern packet\_in { void extract<T>(out T hdr); void extract<T>(out T hdr,in bit<32> n); T lookahead<T>(); void advance(in bit<32> n); bit<32> length(); // parser: begins in special "start" state state start { transition parse\_ethernet; // User-defined parser state state parse\_ethernet { packet.extract(hdr.ethernet); transition select(hdr.ethernet.type) { 0x800: parse\_ipv4; default: accept;

#### Actions, Control Flow & Tables

#### Action

#### UNIVERSITY OF TWENTE.

#### Tables

```

table ipv4_lpm {

key = {

hdr.ipv4.dstAddr: lpm;

}

actions = {

ipv4_forward;

drop;

NoAction;

}

size = 1024;

default_action = NoAction();

}

```

#### Applying Tables in Controls

Deparsing

Emit headers in front of payload.

```

// packet_out: extern for output packet

extern packet_out {

void emit<T>(in T hdr);

}

apply {

// insert headers into pkt if valid

packet.emit(hdr.ethernet);

}

```

Repository

- Instructions on gitlab:

- https://gitlab.utwente.nl/m7717102/p4-labs-2025

- Fork of P4 language tutorials

What you need to do

- Assignment 1

- Basic Forwarding

- Basic Tunneling

- Assignment 2

- P4Runtime

- Assignment 3

- Firewall

- Assignment 4

- Load balancing

- Controlled load balancing

How to carry them out

- Follow tutorial instructions (in the README files)

- Add comments to P4 code briefly explaining

- What the code does

- Why you did it that way

- Parts of the cheat sheet that you used

- Only use the cheat sheet, do not use the answers (obviously)

- Upload P4 code to Canvas

Signing off

- Demonstrate your code and its behavior

- Briefly explain what you did

- Might ask more in-depth questions

Sessions

- Monday 6th October: Sign-off session #1

- Thursday 3rd November: Sign-off session #2

#### Grading:

Pass if everything signed off on Monday 3rd November

Tips

- Assume you need around **16 hours** to do all the assignments

- ⇒ around half the work needs to be done outside the lab sessions

- Try to have the Assignments 1 & 2 finished at the first lab session

- Fully read what you have to implement before actually writing any code

- Understand the files you have to edit

- In the VM, if Backspace suddenly does not work anymore: use CTRL + Backspace

#### Links

P4 resources: <a href="http://P4.org/learn">http://P4.org/learn</a>

Assignment Repo: <a href="https://gitlab.utwente.nl/m7717102/p4-labs-2025">https://gitlab.utwente.nl/m7717102/p4-labs-2025</a>

V1Model source code and docs:

https://github.com/p4lang/p4c/blob/main/p4include/v1model.p4